Flexibility, Scalability and Performance of the RAW Network Router

Umar Saif, James W. Anderson, Anthony Degangi & Anant Agarwal

The network processing industry is continuously faced by four challenges: high-performance, cost, scalability and programmability. In order to remain competitive in a market characterized by an ever-increasing demand for throughput and functionality, network routers must provide high, predictable throughput without confounding programmability or scalability. However, high-performance network routers are typically built using custom-designed hardware. As a consequence, network routers are expensive, offer limited programmability and must be frequently redesigned to keep up with changes in routing standards, throughput requirements and algorithmic innovations. In contrast, network routers based on a traditional general-purpose architecture are cost-effective due to economies of scale and offer greater degree of flexibility for upgrading and extending the functionality of the router, but fail to provide the level of performance warranted by high-performance routing. In this work we investigate the suitability of general-purpose tiled-architectures for high-performance network routing.

Tiled-architectures are based on a modular, scalable design, offer the same degree of programmability as traditional general-purpose architectures, and claim to offer architectural primitives that are better suited to stream-oriented parallel applications. However, whether such architectures can also deliver performance comparable to custom-designed ASICs is an open question. In this work, we aim to answer this question in the context of high-speed network routing -- a domain traditionally dominated by custom-designed ASICs. Specifically, this work aims to answer the following question: "Can a software-based router on a general-purpose tiled-architecture achieve a performance comparable to a custom-designed network router?"To answer this question, we have developed a continuum of router architectures on the RAW microprocessor. The routers presented in this paper are based on a decentralized, scalable architecture and can achieve a throughput of more than 14 Gb/sec -- an order of magnitude improvement over previous software routers on traditional general-purpose architectures and at least 4 times faster than Intel's IXP1200. Additionally, the router designs presented in this paper interoperate with a variety of line-cards and memory devices, can be easily extended in software with additional functions for packet processing, and can implement a range of policies for quality of service.

How

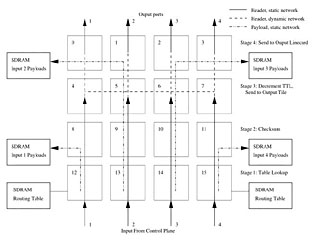

The router architecture exploits the raw's rich programmable interconnects, internal speed-up and explicit parallelism in the raw chip to achieve high-performance without specialized hardware support for router-specific functions. Figure 1 shows an example layout of the router functions on the raw chip.

This example layout has four static pipelines, each entailing four stages corresponding to a row of tiles. This layout uses a combination of dynamic routing, pipelining and static DMA channels to achieve high performance.

Figure 1 : Layout of Data Plane

Research Support

This project is supported by MIT's project Oxygen.

The Stata Center, Building 32 - 32 Vassar Street - Cambridge, MA 02139 - USA tel:+1-617-253-0073 - publications@csail.mit.edu (Note: On July 1, 2003, the AI Lab and LCS merged to form CSAIL.) |