# LABORATORY FOR COMPUTER SCIENCE

MIT/LCS/TM-241

# TWO FUNDAMENTAL ISSUES IN MULTIPROCESSING: THE DATAFLOW SOLUTION

Arvind

Robert A. lannucci

August 1985

## Two Fundamental Issues in Multiprocessing: The Dataflow Solution

This paper, also published as Computation Structures Group Memo 226-3, supercedes the paper previously published as MIT/LCS/TM-241.

August 1985

Arvind Robert A. Iannucci

This report describes research done at the Laboratory for Computer Science of the Massachusetts Institute of Technology. Funding forthe Laboratory is provided in part by the Advanced Research Projects Agency of the Department of Defense under the Office of Naval Research contract N00014-84-K-0099. The second author is supported by the International Business Machines Corporation.

#### Abstract

To exploit the parallelism inherent in algorithms, any multiprocessor system must address two very basic issues - long memory latencies and waits for synchronization events. It is argued on the basis of the evolution of high performance computers that the processor idle time induced by memory latency and synchronization waits cannot be reduced simultaneously in von Neumann style multiprocessors. Dataflow architectures are offered as an alternative because, given enough parallelism in a program, they can reduce both latency and synchronization costs.

Key words and phrases: caches, cache coherence, dataflow architectures, hazard resolution, Istructure storage, instruction pipelining, LOAD/STORE architectures, multiported memories, multiprocessors, von Neumann architecture.

This paper is a major revision of our previous work on the subject:

Version

Title

CSG Memo 226-1

A Critique of Multiprocessing von Neumann Style

Presented at the 10th International Symposium on Computer Architecture,

Stockholm, Sweden, June 14-17, 1983

CSG Memo 226-2

Two Fundamental Issues in Multiprocessing: the Dataflow Solution

Reprinted as MIT/LCS/TM/241

September, 1983

# Table of Contents

| Importance of Processor Architecture                           | 1           |

|----------------------------------------------------------------|-------------|

| 1.1. The Structural Model                                      | 1           |

| 1.2. The Operational Model                                     | 3           |

| 1.3. The Two Fundamental Issues                                | 3           |

| 2. Multiprocessing based on von Neumann Processors             |             |

| 2.1. Pipelined von Neumann Processors                          | 5<br>7<br>9 |

| 2.2. Load/Store Architectures                                  | 9           |

| 2.2.1. Difficulties in Instruction Pipelining                  | 9           |

| 2.2.2. Hazard Resolution and Memory Latency                    | 11          |

| 2.2.3. Summary                                                 | 12          |

| 2.3. Latency Reduction Methods and their Cost                  | 12          |

| 2.3.1. Caches                                                  | 12          |

| 2.3.2. Pipelined Memory Systems                                | 14          |

| 2.4. Synchronization Methods and their Cost                    | 15          |

| 2.4.1. Global Scheduling on Synchronous machines               | 15          |

| 2.4.2. Interrupts and Low Level Context Switching              | 16          |

| 2.4.3. Semaphores and the Ultracomputer                        | 17          |

| 2.5. Lessons Learned thus Far                                  | 18          |

| 3. The Dataflow Approach                                       | 18          |

| 3.1. Dataflow graphs                                           | 18          |

| 3.2. Static Allocation of Storage for Operands                 | 20          |

| 3.3. The Tagged-Token Dataflow Processor                       | 22          |

| 3.3.1. Dynamic Allocation of Operand Store                     | 22          |

| 3.3.2. Executing a Procedure on Several Processors             | 23          |

| 3.3.3. Creating Contexts for Procedure Invocations             | 25          |

| 3.4. Data Structure Operations and I-Structures                | 26          |

| 3.4.1. Functional Operations on Data Structures                | 26          |

| 3.4.2. I-Structures                                            | 27          |

| 3.5. Simultaneously Reducing Latency and Synchronization Costs | 28          |

| Future Evolution of Multiprocessors                            | 30          |

| 4.1. The Denelcor HEP: A Hybrid Architecture                   | 31          |

| 4.2. Procedure Level Dataflow                                  | 32          |

| 5. Acknowledgments                                             | 32          |

# List of Figures

| Figure 1-1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Structural Model of a Multiprocessor                                      | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operational Model of a Multiprocessor                                     | 3  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The von Neumann Processor (from Gajski and Peir [16])                     | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Traditional Interpretation of Instructions                                | 7  |

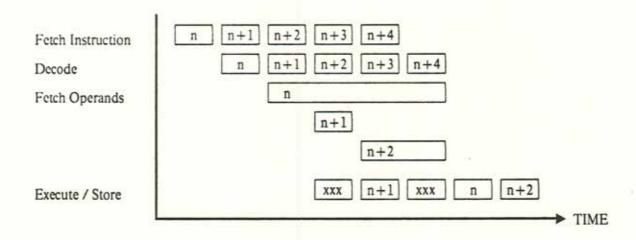

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Overlapping of Instruction Fetch / Decode                                 | 7  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Totally Pipelined Execution                                               | 8  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Variable Operand Fetch Time                                               | 9  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hazard Avoidance at the Instruction Decode Stage                          | 10 |

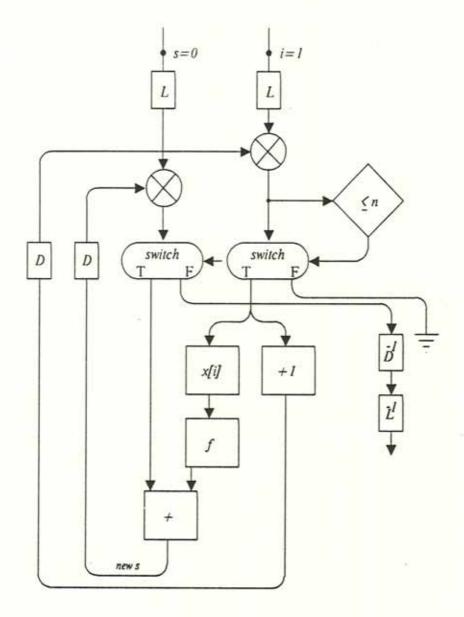

| The second secon | Compilation of the Loop Expression for $\Sigma$ f(x <sub>i</sub> )        | 19 |

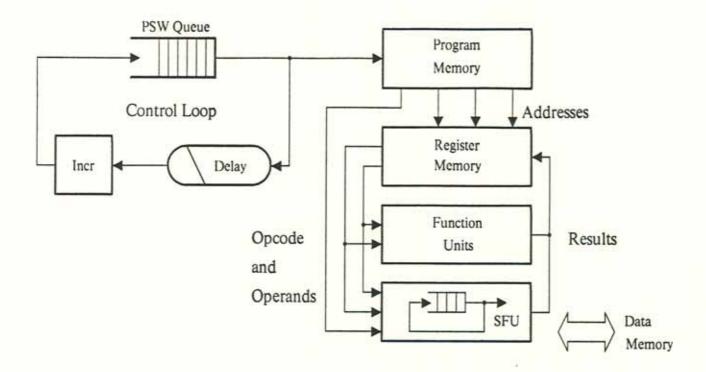

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | One Processing Element of the Static Dataflow Machine (adapted from [11]) | 21 |

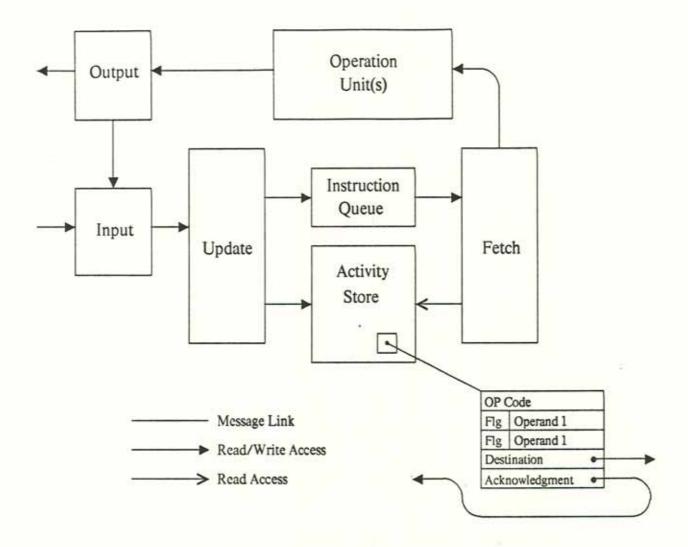

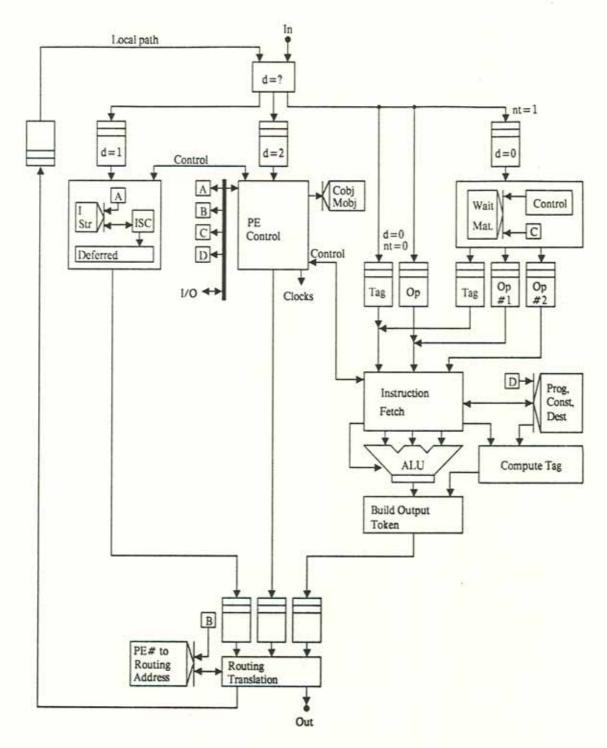

| A 10172711                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Block Diagram of a Tagged-Token Dataflow Processor                        | 24 |

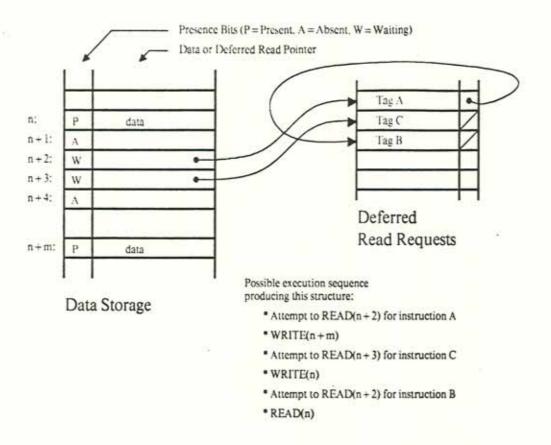

| P. Co. St. Co. Co. Co. Co. Co. Co. Co. Co. Co. Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-Structure Storage                                                       | 28 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Detailed Diagram of the Tagged Token Processing Element                   | 29 |

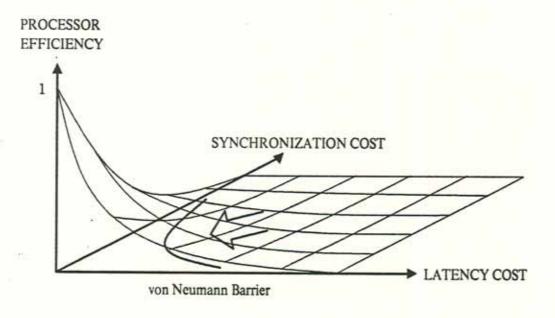

| Figure 4-1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The Latency-Synchronization-Efficiency Space                              | 30 |

| 100000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Latency Toleration and Synchronization in the HEP                         | 31 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |    |

## Two Fundamental Issues in Multiprocessing: The Dataflow Solution

#### 1. Importance of Processor Architecture

It is generally believed that processor architecture is of little importance in designing parallel machines. To show the fallacy of this assumption, we will discuss two basic issues, namely, memory and communication latency and synchronization, that any architect of a scalable, general purpose parallel machine must confront. We believe these issues to be as limiting and as fundamental as those imposed by circuit technology (power consumption, heat dissipation, length and thickness of wires, packaging, etc.). We further believe that parallel machines of the next generation are more likely to hit these architectural limits than the technology-imposed limits. As such, they are more immediately relevant.

We are primarily interested in *general purpose parallel computers*, *i.e.*, computers that can exploit parallelism, when present, in any algorithm. Further, we want multiprocessors to be *scalable* in such a manner that adding hardware resources results in higher performance without requiring substantial rewriting of application programs. The benefits of such scalable systems are obvious; the pitfalls in designing them are subtle.

To understand the effect of latency and synchronization on performance, one also needs to understand the execution of programs on parallel machines. First of all, one needs to identify parallel subcomputations in a source program. This can be done with the help of a compiler, via programmer-provided annotations, or both. To exploit this parallelism, a parallel machine must provide run time support for the *creation* and *synchronization* of tasks corresponding to these subcomputations.

In the next few sections we present our framework for addressing the issues of latency and synchronization, and our formal statement of the problem. The framework is based on two abstract and fairly orthogonal views of multiprocessors. One view which deals with the gross hardware organization is embodied in the *structural model*; the other view which deals with the essential elements of parallel programming is embodied in the *operational model*. Our statement of two fundamental issues in multiprocessor design is based on these models.

#### 1.1. The Structural Model

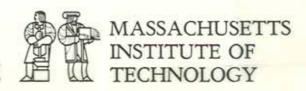

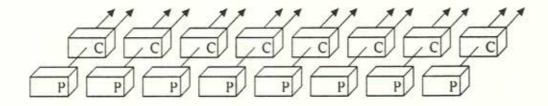

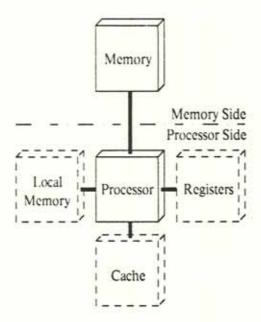

The model shown in Figure 1-1 will be used as the baseline for describing multiprocessor organizations in this paper. It abstracts away the physical packaging and network topology because, as shall become clear later, the design of these aspects of multiprocessors will not affect the main hypothesis of this paper. The *structural model* is made up of three parts:

Processing elements: Modules which perform arithmetic and logical operations on data.

Each processing element (PE) has a single communication port through which all data values are received. Processing elements interact with other processing elements by issuing and responding to synchronizing signals, e.g., WAIT and SEND semaphores,

Figure 1-1: Structural Model of a Multiprocessor

interrupts, etc., and with memory elements by issuing LOAD and STORE instructions embellished as necessary with atomicity modifiers. Processing elements are characterized by the rate at which they can issue and respond to such signals, instructions, and data.

- Memory elements: Modules which store data. Each memory element has a single communication port. Memory elements respond to instructions issued by the processing elements by returning data through the communication port, and are characterized by their total capacity and the rate at which they respond to these instructions.

- Communication elements: Modules which transport data. Each nontrivial communication element has at least three communication ports. Communication elements neither originate nor receive synchronizing signals, instructions, or data; rather, they retransmit such information when received on one of the communications ports to one or more of the other communication ports. Communication elements are characterized by the rate of retransmission, the time taken per retransmission, and the constraints imposed by one retransmission on others, e.g., blocking. The maximum amount of data which may be conveyed on a communication port per unit time is fixed.

A multiprocessor system may be composed by interconnecting each communication port of one module with exactly one other communication port of another module. Processors and memories may only be connected to communication elements. Communication elements may be connected to either processors, memories, or other communication elements. Bus oriented multiprocessors can also be represented in our structural model given that communication elements are capable of broadcast behavior. This aspect of the bus structure can play an important, albeit indirect, role in lowering memory latency as we shall see in section 2.3.1.

#### 1.2. The Operational Model

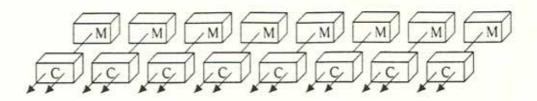

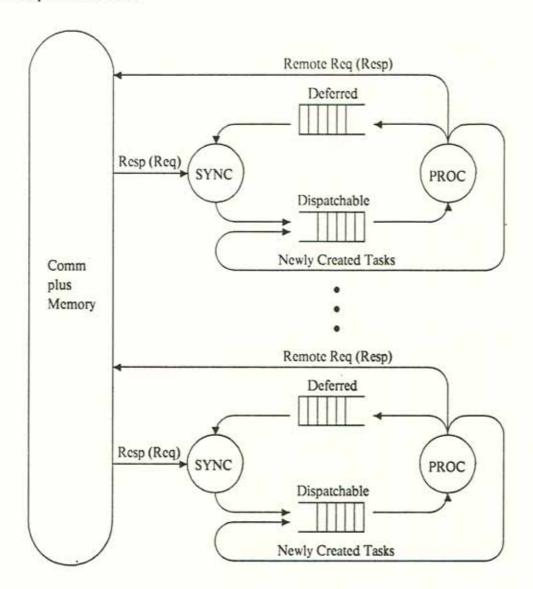

Figure 1-2: Operational Model of a Multiprocessor

To derive the benefits of parallel hardware, a program must be decomposed into basic units of computation which we shall call *computational tasks* or simply *tasks*. One may view these tasks as being units of work as small as machine instructions or as large as procedures comprised of thousands of instructions. Tasks have several interesting properties:

- . They are the smallest unit of independently schedulable work on the machine.

- The set of legal primitive operations a task may perform must include one which is capable of spawning another task.

- Tasks communicate with one another by sending and receiving signals and/or data, e.g., one task produces data which is consumed by another task.

Each task is logically associated with a set of unique names, called its context, to reference task-held resources such as memory locations, registers, etc.

We have chosen to model the operational behavior of a multiprocessor as shown in Figure 1-2. Tasks ready for execution may be queued locally (on a per-PE basis) or globally. When selected, a task will occupy a PE until it can proceed no further because it must wait for a synchronization signal. Some hardware or software scheduling mechanism may also suspend a task and release the PE if, for example, the task makes a nonlocal reference which may take a long time to process. Notice that regardless of whether the PE is released or not, when a task makes a nonlocal request, it is logically suspended, and will wait until the result of the nonlocal reference has been returned. At that point, the task becomes dispatchable once again. One may view the components of the model as operating asynchronously with respect to one another. The queues shown need not adhere to any particular ordering discipline, e.g., FIFO or LIFO. An event to enable or dispatch a task needs a name, such as that of a register or a memory location, and thus, the machinery implied by our operational model must capture the essence of managing task-generated names for both task creation and task synchronization. Hardware design usually dictates the number of names available for synchronization as well as the cost of their use.

#### 1.3. The Two Fundamental Issues

We now discuss issues related to *latency* and *synchronization*, two universal characteristics of multiprocessor organizations.

Latency is the time which elapses between making a request and receiving the associated response. Of immediate interest is memory latency which, in a multiprocessor system, determines the time taken to execute an instruction involving a remote operand reference. A PE in a multiprocessor system faces larger latency than in a uniprocessor system because of the transit time in the communication network between PE's and the memories. When latency cannot be hidden via overlapped operations, a tangible performance penalty is incurred. We will count the cost associated with latency as the total induced processor idle time attributable to the latency. It includes arbitration time, time of flight through the network, and the time required to process the request.

The Operational Model implies that tasks need to communicate with each other. For example, a task may produce a datum which is needed by another task, or may request a resource currently in use. In either case, the sequencing, or *synchronization*, of an event in one task with an event in another is required. The cost associated with such synchronization is also the *induced processor idle time* attributable to synchronization event waiting. It is made up of a fixed time to perform the synchronization operation itself plus the variable time of waiting for the satisfaction of the constraint. If a PE immediately suspends the task causing a synchronization event wait, the cost per synchronization event is fixed.

The performance of a parallel machine is likely to hit an absolute ceiling if adding processors to the machine increases processor idle time due to increased latency and a greater need for synchronization. Thus, we assert that It is necessary to simultaneously minimize the costs of latency and synchronization in order to build a scalable multiprocessor.

One is tempted to assume that the latency issue pertains solely to the hardware organization of the machine, and that the synchronization issue pertains exclusively to the software systems that run on the machine. However, this is not the case. It is likely that attempts to reduce the latency cost will increase the synchronization cost and *vice versa*. In the rest of this paper we will show that

- for multiprocessor organizations based on von Neumann processors, it is impossible to independently minimize both latency cost and synchronization cost, and

- for a class of multiprocessor organizations including dataflow architectures, it is possible

to independently minimize both latency cost and synchronization cost assuming the

program has sufficient parallelism.

In Section 2 we trace the evolution of high performance von Neumann computers to show how reductions in latency costs have been achieved. It is shown that the techniques used for reducing latency costs are either not applicable in the multiprocessor setting or come at the expense of increasing the synchronization cost. Section 3 presents the essential features of dataflow machines, with special emphasis on the MIT Tagged-Token Dataflow machine to show how such architectures can trade parallelism in programs for simultaneous reductions in latency and synchronization costs. In Section 4, we present our view of how multiprocessor architectures should evolve in the future.

Throughout the paper we make references to many planned and existing uniprocessor and multiprocessor architectures. Most, if not all, of these machines were designed to achieve goals other than those set forth here, that is, scaling and programming generality. We have taken the liberty to analyze these architectures using our criteria. In spite of our sometimes less than flattering evaluation, these machines may be enormously successful in meeting their own goals. Note that our intention is to better understand the limits of multiprocessor architectures, and not to make an absolute value judgment on any machine.

#### 2. Multiprocessing based on von Neumann Processors

In this section we begin our study of the evolution of von Neumann architectures. We ask for the reader's indulgence as we begin rather slowly and at a basic level. The points we wish to make are most clearly seen within such a simple, uncluttered framework, and it is for this reason that we reiterate what most readers will view as elementary.

Figure 2-1 depicts the modern day view of the von Neumann computer model (sans I/O) as a mutation of von Neumann's original vision. His description [7] was of a processor-memory pair with most or all of the computation's state residing in the memory. The depicted view emphasizes the migration of state toward the processor side of the processor-memory interconnection. The reasons for this have relevance to both uniprocessor and multiprocessor architectures and are discussed below.

<sup>&</sup>lt;sup>1</sup>We further ask that the reader set aside any technology specific prejudices, e.g., the relative speeds of processors and memories.

Figure 2-1: The von Neumann Processor (from Gajski and Peir [16])

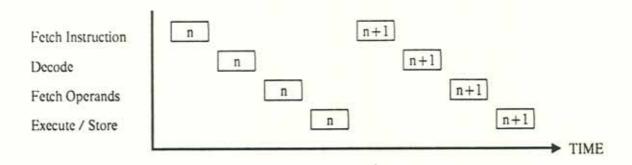

The processor's sole purpose is to repeatedly carry out the following instruction interpretation cycle (see Figure 2-2):

- Fetch an instruction from the memory.

- 2. Decode the instruction.

- (Fetch operands from memory.)

- Execute the decoded instruction using the fetched data.

- 5. (Store results in the memory.)

- Determine the next instruction to be executed.

The steps shown in parentheses are optional for some instructions. In early machines the time taken to go through one iteration of this interpretation cycle was the cycle time of the machine. Different steps in the cycle took different amounts of time. Because memories were relatively slow compared to the processors, time to fetch an instruction and time to fetch and store operands completely dominated the cycle time. Speeding up the Arithmetic Logic Unit was of little use unless the memory access time could be reduced.

The earliest solution to speeding up the machine was to increase the *processor state*, *i.e.*, to provide fast storage on the processor side in the form of registers. Appearance of multiple "accumulators" reduced the number of operand fetches and stores, and index registers dramatically reduced the number of memory references by almost eliminating the need for self modifying code.

Figure 2-2: Traditional Interpretation of Instructions

A later technique involved reducing the number of instructions executed and, hence, the number of instructions fetched. This was accomplished by making the instructions themselves more complex (i.e., defining a richer language). This technique was less successful than adding registers due to difficulty in designing complex control circuitry. Even though the cumulative effect of these two techniques was that programs executed much faster than before, the basic cycle time improved only as a function of improvements in circuit speeds, i.e., technology. The enlarged processor state reduced the number of memory references, but it did not reduce the time lost during memory references and, consequently, did not contribute to an overall reduction in cycle time.

#### 2.1. Pipelined von Neumann Processors

The most successful solution to hiding memory latency is the *pipelined execution* of instructions. The time taken by instruction fetch (and perhaps part of instruction decoding time) can be totally hidden if prefetching is done during the execution phase of the previous instruction (see Figure 2-3). The IBM STRETCH [6] and the Univac LARC [12] represent two of the earliest attempts at implementing this idea. Prefetching can reduce the cycle time of the machine by 20% to 30% depending upon the amount of time taken by the first two steps of the instruction cycle with respect to the complete cycle. However, the effective throughput of the machine cannot increase proportionately because overlapped execution is not possible with *all* instructions.

Figure 2-3: Overlapping of Instruction Fetch / Decode

Instruction prefetching works well when the execution of instruction n does not have any effect on either the choice of instructions to fetch (e.g., as is the case in a BRANCH) or the content of the fetched instruction (e.g., self-modifying code) for instructions n+1, n+2, ..., n+k. The latter case is usually handled by simply outlawing it. However, effective overlapped execution in the presence of BRANCH instructions has remained a problem. Techniques such as prefetching both BRANCH targets have not shown much performance/cost benefits. Lately, the concept of *delayed* BRANCH instructions from microprogramming has been incorporated, with success, in LOAD/STORE architectures (see section 2.2). The idea is to delay the effect of a BRANCH by one instruction. Thus, the instruction at n+1 following a BRANCH instruction at n is always executed regardless of which way the BRANCH at n goes. One can always follow a BRANCH instruction with a NO-OP instruction to get the old effect. However, experience has shown that 70% of the time a useful instruction can be put in that position.

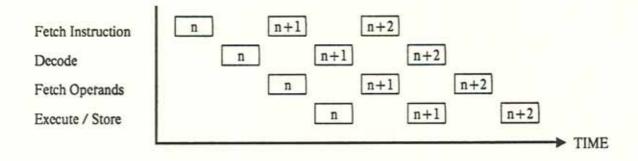

If instructions and data are kept in separate memories (the so-called Harvard architecture, another idea borrowed from microprogramming), it is possible to overlap instruction prefetching with fetching of operands, too. It is also possible to reduce the instruction fetch time by providing a fast instruction buffer. The buffer may be automatically loaded with n instructions in the neighborhood of the referenced instruction (assuming some spatial locality in code references) if the referenced instruction is found to be missing (e.g., the CDC 6600 [31]). To take advantage of either separate instruction memory or instruction buffers, it is necessary to also speed up the operand fetch and execute phases. The two most common techniques for doing this are:

- · providing operand caches or buffers, and

- overlapping the operand fetch and execution phases (Figure 2-4).

If successful<sup>2</sup>, these techniques can reduce the machine cycle time to one fourth or one fifth the cycle time of an unpipelined machine. However, overlapped execution of 4 to 5 instructions in the von Neumann framework presents some serious conceptual difficulties.

Figure 2-4: Totally Pipelined Execution

<sup>&</sup>lt;sup>2</sup>Of course, it is likely that balancing the pipeline under these conditions may require further pipelining of the ALU.

#### 2.2. Load/Store Architectures

Next, we discuss techniques used in machines built by Seymour Cray, e.g., the CDC 6600 [31] and the Cray-1 [28], and more recently, by Reduced Instruction Set Computer (RISC) enthusiasts, e.g., the IBM 801 [26], Berkeley's RISC [25], and Stanford MIPS [20], because of their success in pipelining von Neumann machines.

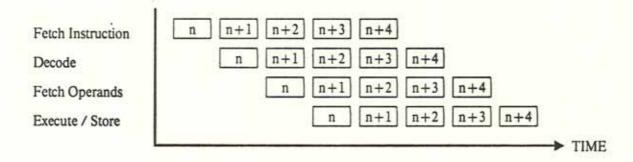

#### 2.2.1. Difficulties in Instruction Pipelining

Designing a well-balanced pipeline requires that the time taken by various pipeline stages be more or less the same, and that the "things", *i.e.*, instructions, entering the pipe be independent of each other. Obviously, instructions of a program cannot be totally independent except for some special trivial cases. Instructions in a pipe are usually related in one of two ways: Instruction n produces data needed by instruction n + k, or only complete execution of instruction n determines the next instruction to be executed (the aforementioned delayed BRANCH problem).

Limitations on hardware resources can also cause instructions to interfere with one another. Consider the case when both instructions n and n+1 require an adder, but there is only one of these in the machine. Obviously, one of the instructions must be deferred until the other is complete. A pipelined machine must be able to temporarily prevent a new instruction from entering the pipeline when there is a possibility of interference with the machine resource requirements of instructions already in the pipe. Detecting and quickly resolving these possibilities of interferences, or *hazards* as they are commonly known, is very difficult with ordinary instruction sets, e.g., IBM 370, VAX 11 or Motorola 68000, due to their complexity.

Figure 2-5: Variable Operand Fetch Time

A further complication in pipelining complex instructions is the variable amount of time taken in each stage of instruction processing (refer to Figure 2-5). Operand fetch in the VAX is one such example: determining the addressing mode for each operand requires a fair amount of decoding, and actual fetching can involve 0 to 2 memory references *per operand*. Considering all possible addressing mode combinations, an instruction may involve 0 to 6 memory references in addition to the instruction fetch itself. A pipeline design that can effectively tolerate such variations is close to impossible.

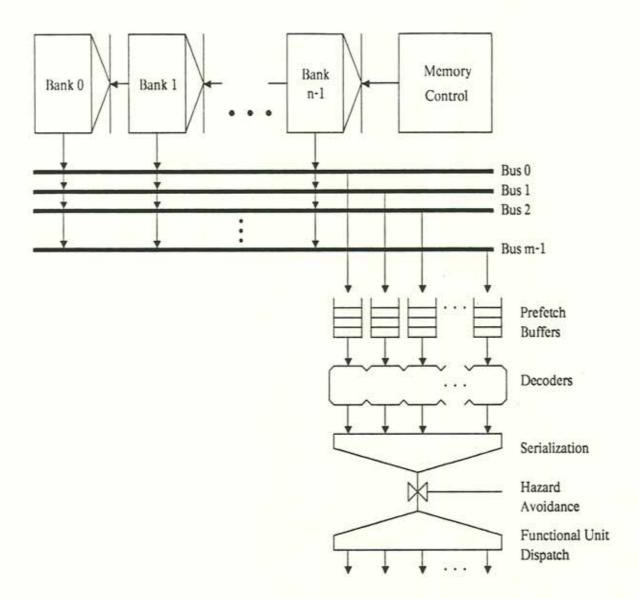

Figure 2-6: Hazard Avoidance at the Instruction Decode Stage

An idea of Seymour Cray (first seen in the CDC 6600) is to design an instruction set in which instructions that refer to memory are separable from those which do not at the instruction decode stage. Such is the case with LOAD/STORE architectures - the only memory reference instructions are those which move data unchanged between the memory and the registers. All other instructions are constrained to use the high speed registers [20, 26, 25]. Further, given that instructions in a pipeline cannot be independent of each other, the design of the pipeline is simpler if processing of an instruction can be stopped at only one stage of the pipeline. In other words, if an instruction gets past some fixed pipe stage, it should be able to run to completion without incurring or creating any previously unanticipated hazards. LOAD/STORE architectures allow for such implementations by using the time between instruction decoding and instruction dispatching for hazard detection and resolution (see Figure 2-6).

#### 2.2.2. Hazard Resolution and Memory Latency

LOAD/STORE architectures are much better at tolerating latencies in memory accesses than other von Neumann architectures. In order to explain this point we will first discuss a simplified model which detects and avoids hazards in a LOAD/STORE architecture similar to the Cray-1. Assume there is a bit associated with every register to indicate that the contents of the register are undergoing a change. The bit corresponding to register R is set the moment we dispatch an instruction that wants to update R. Following this, instructions are allowed to enter the pipeline only if they don't need to reference or modify register R or other registers reserved in a similar way. Whenever a value is stored in R, the reservation on R is removed, and if an instruction is waiting on R, it is allowed to proceed. This simple scheme works only if we assume that registers whose values are needed by an instruction are read before the next instruction is dispatched, and that the ALU or the multiple functional units within the ALU are pipelined to accept inputs as fast as the decode stage can supply inputs<sup>3</sup>. The dispatching of an instruction can also be held up because it may require a bus for storing results in a clock cycle when the bus in needed by another instruction in the pipeline. Whenever BRANCH instructions are encountered, the pipeline is effectively held up until the branch target has been decided.

Notice what will happen when an instruction to load the contents of some memory location M into some register R is executed. Suppose that it takes k cycles to fetch something from the memory. It will be possible to execute several instructions during these k cycles as long as none of them refer to register R. In fact, this situation is hardly different from the one in which R is to be loaded from some functional unit (e.g., the Floating Point multiplier) that takes several cycles to produce the result. These gaps in the pipeline can be further reduced if the compiler reorders instructions such that instructions consuming a datum are put as far as possible from instructions producing that datum. Thus, we notice that machines designed for high pipelining of instructions can hide large memory latencies provided there is local parallelism among instructions.

Some LOAD/STORE architectures have eliminated the need for reservation bits on registers by making the compiler responsible for not scheduling instructions until the time when the result is supposed to be available. The compiler performs this static hazard resolution by assuming deterministic time for each operation (e.g., ADD, LOAD) and inserting NO-OP instructions wherever necessary. Because the instruction execution times are intimately built into the code, any change to the machine's structure (scaling, redesign) will at the very least require changes to the compiler and regeneration of the code. This is obviously contrary to our notion of generality, and hinders portability of software from one generation of machine to the next.

Current LOAD/STORE architectures assume that memory references either take a fixed amount of time (1 cycle in most RISC machines) or that they take a variable but predictable amount of time (as in the Cray-1). In RISC machines, this time is derived on the basis of a cache hit. If the operand is found to be missing from the cache, the pipeline stops. Equivalently, one can think of this as a situation where a clock cycle is *stretched* to the time required. This solution works because, in most of these machines, there can be either one or a very small number of memory references in progress

<sup>&</sup>lt;sup>3</sup>Indeed, in the Cray-1, functional units can accept an input every clock cycle and registers are always read in one clock cycle after an instruction is dispatched from the Decoder.

<sup>&</sup>lt;sup>4</sup>The ability to reorder two instructions essentially means that these instructions can be executed in parallel.

at any given time. For example, in the Cray-1, no more than 4 independent addresses can be generated in any memory cycle. If an address causing a bank conflict is generated, then the pipeline must be stopped. However, any conflict will be cleared in at most 3 cycles.

#### 2.2.3. Summary

Good implementations of LOAD/STORE architectures can effectively pipeline many instructions at a time. Even though instructions are decoded in order, they may finish out of order. If there is sufficient parallelism in the source code and the compiler is good at reordering instructions, latencies of memory accesses can be hidden behind useful ALU work.

Latency cost can be reduced by introducing a cheap synchronization mechanism: reservation bits on processor registers. However, the number of names available for synchronization, i.e., the size of the task's processor-bound context, is precisely the number of registers, and this restricts the amount of parallelism that can be exploited<sup>5</sup>. In order to understand this issue better, consider the case when the compiler decides to use register R to hold two different values at two different instructions say, n and n. This will require n and n to be executed sequentially while no such order may have been necessary in the source code. It would seem that more programmable registers in the architecture will provide more names for synchronization and, hence, a greater opportunity for tolerating latency. The obvious disadvantage of relying on this scheme is clear: the machine's ability to manipulate such names is bound tightly into the instruction set and thereby limits scalability.

It would be desirable if all the techniques developed for uniprocessors carried over directly to multiprocessor architecture. In fact, they do not. It was mentioned earlier that memory latency in a multiprocessor is going to be larger and less predictable than in a uniprocessor system, and additionally that multiprocessor systems must support some mechanism for the synchronization of computational tasks. The method of synchronization used for reducing latency is usually not used for synchronization at the programming level. In fact, we will show that low cost synchronization at the programming level calls for small, instead of large, processor state. In the following sections we discuss the methods of reducing the *induced processor idle time* due to latency and synchronization that have been either implemented or suggested for multiprocessor systems.

#### 2.3. Latency Reduction Methods and their Cost

#### 2.3.1. Caches

Let us assume that all memory modules in a multiprocessor form one global address space and that any processor can read any word in the global address space. This immediately brings up a number of problems:

The time to fetch an operand may not be constant because some memories may be "closer" than others in the physical organization of the machine.

<sup>&</sup>lt;sup>5</sup>It is interesting to observe in passing that all high performance machines seem to be based on general register architectures rather than on stack architectures. One possible explanation is that, given the same amount of fast storage, a stack machine has far fewer names available to uniquely identify synchronization events and is therefore poorer at trading synchronization cost for latency cost.

- No useful bound on the worst case time to fetch an operand may be possible at machine design time because of the scalability assumption.

- If a processor were to issue several (pipelined) memory requests to different remote memory modules, the responses may arrive out of order.

Some multiprocessors, e.g., Cm\* [15] have avoided rather than solved these problems by making the simplifying assumption that a memory request would not be issued until the previous response had been received. Not surprisingly, even running a program with tremendous parallelism, Cm\* researchers discovered that the problem took longer to complete if more than 8 to 10 processors were used [15]. We think a likely reason is that processor idle time induced by the increase in memory latency could not be recovered by additional processing power.

LOAD/STORE architectures can solve the problems mentioned above to a limited degree. However, a general solution for accepting out of order memory responses requires a synchronization mechanism to match responses with the destination registers (names in the task's context) and the instructions waiting on that register. The Denelcor HEP [21] is one of the very few architectures which has tried to provide such mechanisms in the von Neumann framework. However, the architecture of the HEP is sufficiently different from von Neumann architectures as to warrant a separate discussion (see section 4).

The most popular way of circumventing the latency problem is to employ a local cache in a processor to keep the contents of the most recently used memory locations. This highly successful idea from uniprocessors suffers a great deal in the multiprocessor setting due to a problem called cache coherence. Censier and Feautrier [8] define the problem as follows: "A memory scheme is coherent if the value returned on a LOAD instruction is always the value given by the latest STORE instruction with the same address." In a multiprocessor context, it is easy to see that this may lead to difficulties.

Suppose we have a two-processor system tightly coupled through a single main memory. Each processor has its own cache, to which it has exclusive access. Suppose further that two tasks are running, one on each processor, and we know that the tasks are designed to communicate through one or more shared memory cells. In the absence of caches, this scheme can be made to work. However, if it so happens that the shared address is present in both caches, the individual processors can read and write the address and *never* see any changes caused by the other processor. Using a store-through design instead of a store-in design does not solve the problem either. What is logically required is a mechanism which, upon the occurrence of a STORE to location x, invalidates all other cached copies of location x wherever they may occur, and guarantees that subsequent LOADs will get the most recent (cached) value. This can incur significant overhead in terms of decreased memory bandwidth. All solutions to the cache coherence problem center around reducing the cost of detecting (or rather avoiding) the possibility of cache incoherence, and such solutions seem to work only for bus oriented machines. Some of these are discussed next.

There have been many proposals for solving the coherence problem by using a *logically* centralized directory for all cached data. Each entry reflects the state (e.g., private, shared, etc.) of the associated cache quantum, and is responsible for guaranteeing that coherence is not violated. Implementations of this idea are generally intractable except possibly in the domain of bus oriented multiprocessors. Relying on the broadcasting capability of a bus, it is easy to see how all caches can

purge entry x if a processor attempts a STORE to x (the so-called *snoopy bus*).

In such a system at most one STORE operation can go on at a time in the whole system and, therefore, system performance is going to be a strong function of the bus's ability to handle the coherence-maintaining traffic. It is possible to improve upon this solution if some more information is kept with each cache entry. Suppose entries are marked "shared" or "non-shared". A processor can freely read shared entries but an attempt to STORE into a shared entry immediately causes that address to appear on the snoopy bus. That entry is then deleted from all the other caches and is marked "non-shared" in the processor that had attempted the STORE. Similar action takes place when the word to be written is missing from the cache. Of course, the main memory must be updated before purging the private copy from any cache. When the word to be read is missing from the cache, the snoopy bus may have to first reclaim the copy privately held by some other cache before giving it to the requesting cache. The status of such an entry will be marked as shared in both caches. The advantage of keeping shared/non-shared information with every cache entry is that the snoopy bus comes into action only on cache misses and STOREs to shared locations, as opposed to all LOADs and STOREs. Even if these solutions work satisfactorily, bus oriented multiprocessors are not of much interest to us because of their obvious limitations in scaling.

As far as we can tell there are no known solutions to cache coherence for non bussed machines. It would seem reasonable that one needs to make caches partially visible to the programmer by allowing him to mark data (actually addresses) as shared or not shared. In addition, instructions to flush an entry or a block of entries from a cache have to be provided. Cache management on such machines is possible only if the concept of shared data is well integrated in the high level language or the programming model. Though it may not be obvious, often a direct trade off exists between decreasing the parallelism and increasing the cachable or non shared data. Schemes have also been proposed to explicitly interlock a location for writing or to bypass the cache (and flush it if necessary) on a STORE; in either case, the performance goes down rapidly as the machine is scaled. Ironically, in solving the latency problem via multiple caches, we have introduced the synchronization problem of keeping caches coherent.

#### 2.3.2. Pipelined Memory Systems

One can observe from the Cray-1 and other machines that there is an asymmetry between a heavily pipelined processor and a non-pipelined memory system. Memory systems continue to be slow relative to processors built with comparable technologies, and thus, are usually the performance limiting factor. Interleaving as a technique for reducing apparent access time is unsuitable as a general solution because of sensitivities to addressing patterns.

We have done some initial investigations over the past year into the architecture of pipelined memory systems aimed at solving this problem. If memory systems were designed to accept memory references in a pipelined manner with a large capacity to hold memory requests, stretching of the clock cycle as described in section 2.2.2 can be avoided. To exploit a pipelined memory in its full generality requires a mechanism such as reservation bits to provide fine-grained synchronization rather than relying on a rather complex compiler to predict machine configuration dependent data arrival times. The benefits, however, should be clear.

#### 2.4. Synchronization Methods and their Cost

We turn from our very hardware-intensive view of multiprocessors to the issues of programming a multiprocessor. From this, we will reason about architectural implications of software systems on the underlying hardware. A general model of parallel programming must assume that tasks are created dynamically during a computation, and die after having produced and consumed data. Situations in parallel programming which require task synchronization include the following non-orthogonal basic operations:

- Forks and Joins: The join operation forces a synchronization event indicating that two

tasks which had been started earlier by some forking operation, have in fact completed.

- Producer-Consumer: A task produces a data structure that is read by another task. If producer and consumer tasks are executed in parallel, synchronization is needed to avoid the read-before-write race.

- Mutual Exclusion: Non-deterministic events which must be processed one at a time, e.g., serialization in the use of a resource.

In order to understand the effect of hardware synchronization on software methodology, consider the case wherein the fixed cost of synchronization is high, say equivalent to the time taken by 10 ordinary instructions. Under such conditions it will not pay to exploit producer-consumer parallelism on an element-by-element basis. Rather, one would first produce n (>> 10) elements and then signal the consumer to start consuming. The same procedure would be repeated after producing the next n elements. This way, the cost of synchronization would be kept low by perhaps inducing some extra idle time on the processor on which the consumer task executes. The choice of n certainly depends on the machine and deeply affects how one would write code. If the elements are produced and consumed in somewhat irregular order, or if the data structure comprising the elements is nonuniform, it may be practically impossible to write code to exploit parallelism given certain types of synchronization mechanisms.

#### 2.4.1. Global Scheduling on Synchronous machines

If a multiprocessor is totally synchronous, then it is at least conceptually possible to prepare a master plan in which instructions for every moment on every processor are specified. An analogy can be made between programming such a multiprocessor and coding a horizontally microprogrammed machine. Recently there have been advances in compiling for such machines which have caused several machine proposals to appear [14, 27].

While these machines are able to resolve run-time sharing conflicts by moving them to compile time and are usually able to plan memory references and control transfers in advance of the need (e.g., the delayed BRANCH), these machines suffer from their special-purpose nature. Except in the simplest of cases, compilers require "hints" from the programmer or, in some cases, rely on luck (and hardware interlocks) in doing the code generation. Clearly, these machines are not well suited to real-time computations which involve nondeterministic situations or computations requiring dynamic resource (e.g., memory) management.

We believe that this technique is effective in its currently-realized context - special purpose computation with a small number (4 to 8) of processors, but the technique is not sufficiently general as to allow significant scaling up. Software problems associated with this approach will be

overwhelming far before the hardware cost of latency and synchronization plays any significant role in scaling such machines.

#### 2.4.2. Interrupts and Low Level Context Switching